## University of New Hampshire University of New Hampshire Scholars' Repository

Master's Theses and Capstones

Student Scholarship

Winter 2007

# Software-defined radio using LabVIEW and the PC sound card: A teaching platform for digital communications

Jose Carlos Lanzoni University of New Hampshire, Durham

Follow this and additional works at: https://scholars.unh.edu/thesis

#### **Recommended Citation**

Lanzoni, Jose Carlos, "Software-defined radio using LabVIEW and the PC sound card: A teaching platform for digital communications" (2007). *Master's Theses and Capstones*. 334. https://scholars.unh.edu/thesis/334

This Thesis is brought to you for free and open access by the Student Scholarship at University of New Hampshire Scholars' Repository. It has been accepted for inclusion in Master's Theses and Capstones by an authorized administrator of University of New Hampshire Scholars' Repository. For more information, please contact Scholarly.Communication@unh.edu.

## SOFTWARE-DEFINED RADIO USING LABVIEW AND THE PC SOUND CARD: A TEACHING PLATFORM FOR DIGITAL COMMUNICATIONS

ΒY

#### JOSE CARLOS LANZONI

B.S.E.E., University of New Hampshire, 2002

#### THESIS

Submitted to the University of New Hampshire

In Partial Fulfillment of

The Requirements for the Degree of

Master of Science

in

Electrical Engineering

December, 2007

UMI Number: 1449592

Copyright 2007 by Lanzoni, Jose Carlos

All rights reserved.

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

##

UMI Microform 1449592 Copyright 2008 by ProQuest LLC. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346

### ALL RIGHTS RESERVED

c 2007

Jose Carlos Lanzoni

This thesis has been examined and approved.

Thesis Advisor, Michael J. Carter, Associate Professor of Electrical and Computer Engineering

A Chaml en

Kent A. Chamberlin, Professor of Electrical and Computer Engineering

W. Thomas Miller, Professor of Electrical and **Computer Engineering**

December, 11, 2007 Date

#### DEDICATION

This work is dedicated to my wife, Neide. Thank you for all the support you provided me to accomplish this project. I also dedicate this to my parents.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my thesis advisor, Dr. Michael J. Carter, for the guidance, encouragement, and the assistance on the development of this thesis. I am also grateful to my dissertation committee: Dr. Kent Chamberlin and Dr. Thomas Miller. They provided valuable comments and suggestions to improve this work.

I would like acknowledge Jonathan Beckwith and Mathew Plante. They supplied me with many insights from their work. Also, I would like to acknowledge Robert Cinq-Mars for his friendly assistance with LabVIEW at the University of New Hampshire.

Finally, I would like to thank my family and my friends for their support during these years (Analia, Heloisa, Erik, Adilson, Rafaela, Matteo, Giulia, Dal, Maurik, Daniel, Bel, Lena, Inês, Daniel, Ricardo, Wladia, Mari, Humberto, Roberta, Cassiano, Leticia, Valentina, Elias, Claudia, Evilene, Carina, James, Tyrso, Heloisa, Fabricio, Rosangela, Edward, Hudson, Luciano, Isabel). The friendship built during my time at UNH has proven to be an invaluable joy in my life. In special, I would like to thank Edinaldo Tebaldi, Fernando Santo, and Sergio dos Santos, for sharing their supportive comments and discussions in so many circumstances.

## TABLE OF CONTENTS

•

| DEDICATION       | iv         |

|------------------|------------|

| ACKNOWLEDGEMENTS | v          |

| LIST OF FIGURES  | <b>x</b> i |

| ABSTRACT         | xv         |

| CHAPTER                                                  | PAGE |

|----------------------------------------------------------|------|

|                                                          | 1    |

| 1. TEACHING DIGITAL COMMUNICATION: THE LABORATORY        | 2    |

| 1.1 How Students Learn: Learning Styles                  | 3    |

| 1.2 Issues in a Communications Laboratory                | 3    |

| 1.3 Objectives and Proposed System                       | 4    |

| 1.4 Document Organization                                | 5    |

| 2. SOFTWARE-DEFINED RADIO USING LABVIEW AND THE PC'S SOU | ٧D   |

| CARD AS A DIGITAL COMMUNICATION TEACHING SYSTEM          | 7    |

| 2.1 Digital Modulations                                  | 8    |

| 2.2 Software-Defined Radios                              | 13   |

| 2.3 The LabVIEW Graphical Environment                    | 14   |

| 2.4 SDR Using LabVIEW                                    | 17   |

| 2.5 The Flex-Radio Systems SDR-1000 Platform             | 22   |

| 2.6 Laboratory Experiments24                             |

|----------------------------------------------------------|

| 2.7 Conclusion26                                         |

| 3. DIGITAL COMMUNICATION SYSTEMS AND THE SDR             |

| 3.1 The Typical Digital Communication System Structure27 |

| 3.1.1 Source Coding                                      |

| 3.1.2 Channel Coding29                                   |

| 3.1.3 Modulation29                                       |

| 3.1.4 Up Conversion                                      |

| 3.1.5 Channel                                            |

| 3.1.6 Down Conversion                                    |

| 3.1.7 Demodulation                                       |

| 3.1.8 Channel Decoding30                                 |

| 3.1.9 Source Decoding                                    |

| 3.1.10 Tools Used in a Digital Communication System      |

| 3.2 SDR in a Digital Communication System                |

| 3.3 Remarks                                              |

| 4. THE 4 QAM SDR TRANSCEIVER: USER INTERFACE AND         |

| OPERATION                                                |

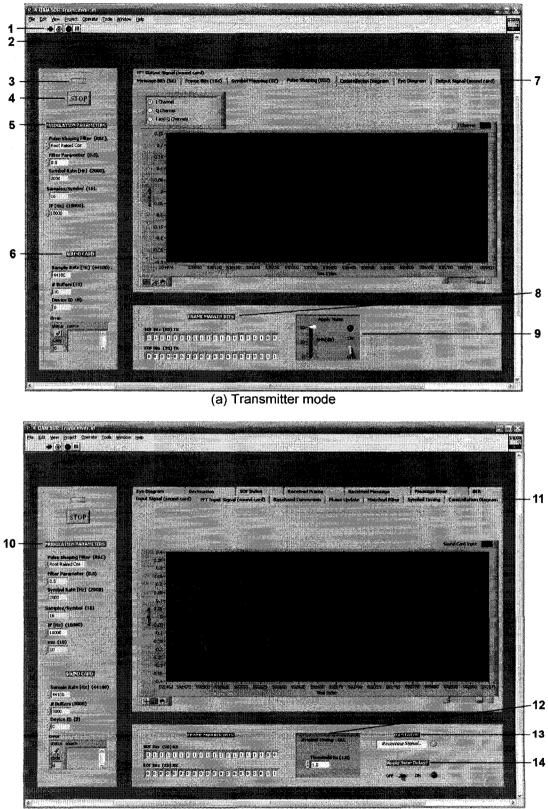

| 4.1 Front Panel and System Description                   |

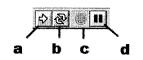

| 4.1.1 Execution Control                                  |

| 4.1.2 Transmitter/Receiver Mode Tabs                     |

| 4.1.3 ON Led Indicator                                   |

| 4.1.4 Stop Button                                        |

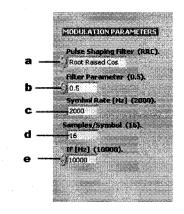

| 4.1.5                                                       | Modulation Parameters in Transmitter Mode                                                                                              | 39                               |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

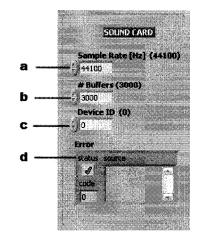

| 4.1.6                                                       | Sound Card Parameters                                                                                                                  | 40                               |

| 4.1.7                                                       | Graph Display Tabs in Transmitter Mode                                                                                                 | 41                               |

| 4.1.8                                                       | Frame Marker Bits in Transmitter                                                                                                       | 42                               |

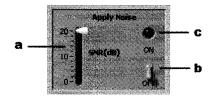

| 4.1.9                                                       | Apply Noise                                                                                                                            | 43                               |

| 4.1.10                                                      | Modulation Parameters in Receiver Mode                                                                                                 | 43                               |

| 4.1.11                                                      | I Graph Display Tabs in Receiver Mode                                                                                                  | 44                               |

| 4.1.12                                                      | 2 Symbol Timing – DLL                                                                                                                  | 46                               |

| 4.1.13                                                      | RX Status                                                                                                                              | 46                               |

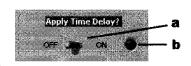

| 4.1.14                                                      | Apply Time Delay Control                                                                                                               | 46                               |

| 4.2 The 4                                                   | QAM SDR Transceiver Operation                                                                                                          | 47                               |

|                                                             |                                                                                                                                        |                                  |

| 5. THE 4 QA                                                 | AM SDR TRANSCEIVER: THEORY AND LABVIEW CODE                                                                                            |                                  |

|                                                             | AM SDR TRANSCEIVER: THEORY AND LABVIEW CODE                                                                                            | 50                               |

| IMPLEME                                                     |                                                                                                                                        |                                  |

| IMPLEME<br>5.1 Quad                                         | NTATION                                                                                                                                | 50                               |

| IMPLEME<br>5.1 Quad<br>5.2 Trans                            | INTATION                                                                                                                               | 50<br>53                         |

| IMPLEME<br>5.1 Quad<br>5.2 Trans<br>5.2.1                   | NTATION<br>rature Signals                                                                                                              | 50<br>53<br>54                   |

| IMPLEME<br>5.1 Quad<br>5.2 Trans<br>5.2.1<br>5.2.2          | ENTATION<br>rature Signals<br>mitter Structure<br>Frame Generation                                                                     | 50<br>53<br>54<br>56             |

| IMPLEME<br>5.1 Quad<br>5.2 Trans<br>5.2.1<br>5.2.2<br>5.2.3 | ENTATION<br>rature Signals<br>mitter Structure<br>Frame Generation<br>Differential Encoding.                                           | 50<br>53<br>54<br>56<br>59       |

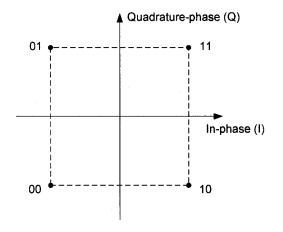

| IMPLEME<br>5.1 Quad<br>5.2 Trans<br>5.2.1<br>5.2.2<br>5.2.3 | ENTATION<br>rature Signals<br>mitter Structure<br>Frame Generation<br>Differential Encoding<br>Bits to Symbol Mapping                  | 50<br>53<br>54<br>56<br>59<br>60 |

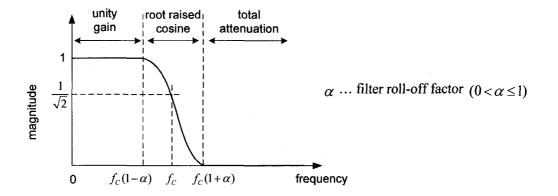

| IMPLEME<br>5.1 Quad<br>5.2 Trans<br>5.2.1<br>5.2.2<br>5.2.3 | ENTATION<br>rature Signals<br>mitter Structure<br>Frame Generation<br>Differential Encoding<br>Bits to Symbol Mapping<br>Pulse Shaping | 50<br>53<br>54<br>56<br>60<br>61 |

|           | 5.2.4.4 Pulse Shaping implementation in the 4 QAM     |     |

|-----------|-------------------------------------------------------|-----|

|           | SDR Transceiver                                       | 66  |

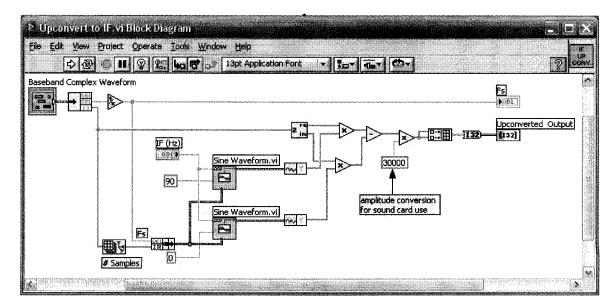

| 5.2.5     | Conversion to IF                                      | 67  |

| 5.2.6     | Sound Card Output                                     | 68  |

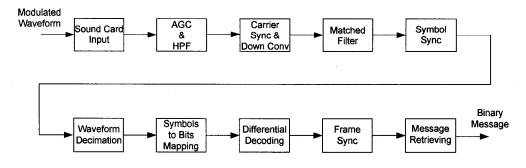

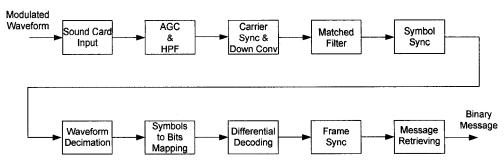

| 5.3 Rece  | iver Structure                                        | 70  |

| 5.3.1     | Sound Card Input                                      | 71  |

| 5.3.2     | Automatic Gain Control (AGC) and High Pass Filtering  |     |

|           | (HPF)                                                 | 72  |

| 5.3.3     | Carrier Synchronization and Down Conversion           | 72  |

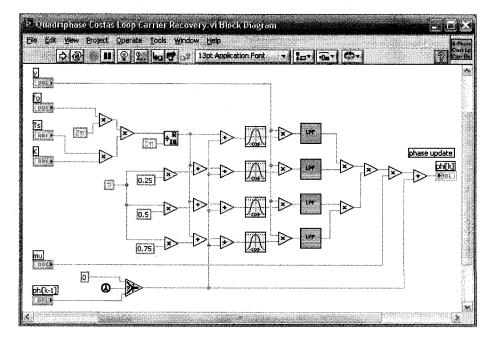

|           | 5.3.3.1 The Costas Loop for 4 QAM                     | 74  |

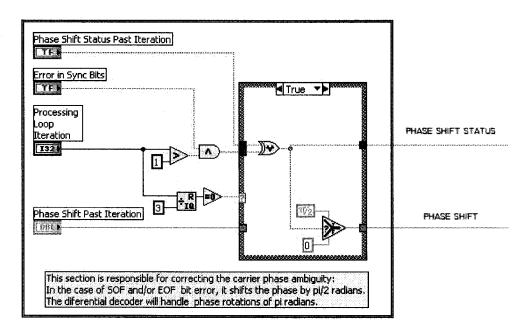

|           | 5.3.3.2 Phase Ambiguity Resolution                    | 80  |

|           | 5.3.3.3 Carrier Synchronization and Down Conversion C | ode |

|           | Implementation                                        | 81  |

| 5.3.4     | Matched Filter                                        | 88  |

| 5.3.5     | Symbol Synchronization                                | 89  |

|           | 5.3.5.1 The Delay-Locked Loop (DLL) Algorithm         | 90  |

| 5.3.6     | Waveform Decimation                                   | 94  |

| 5.3.7     | Symbol to Bits Mapping                                | 97  |

| 5.3.8     | Differential Decoding                                 | 99  |

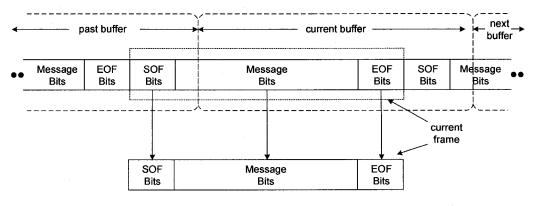

| 5.3.9     | Frame Synchronization and Alignment                   | 100 |

| 5.3.1     | 0 Message Retrieving                                  | 104 |

| 5.4 Rem   | arks                                                  | 107 |

| 6. CONCLU | ISION                                                 |     |

## 5.2.4.4 Pulse Shaping Implementation in the 4 QAM

| LIST OF REFERENCES                     | 112 |

|----------------------------------------|-----|

| APPENDICES                             | 114 |

| APPENDIX A: LABORATORY EXPERIMENTS     | 115 |

| APPENDIX B: 4 QAM SDR TRANSCEIVER CODE | 163 |

х

### LIST OF FIGURES

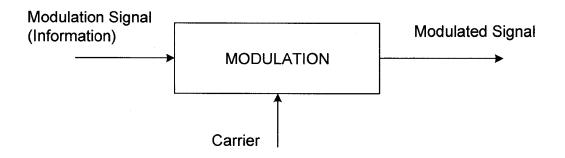

| Figure 2-1:  | Modulation                                                   | 8  |

|--------------|--------------------------------------------------------------|----|

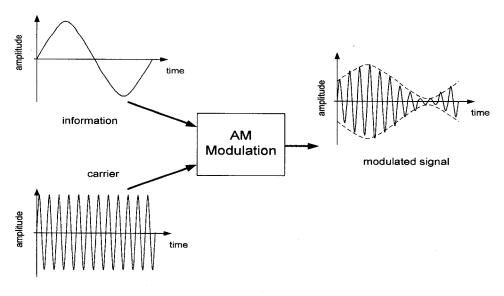

| Figure 2-2:  | Amplitude Modulation (AM)                                    | 9  |

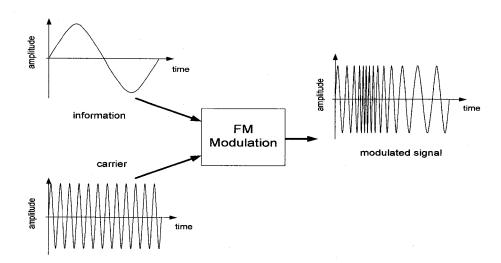

| Figure 2-3:  | Frequency Modulation (FM)                                    | 9  |

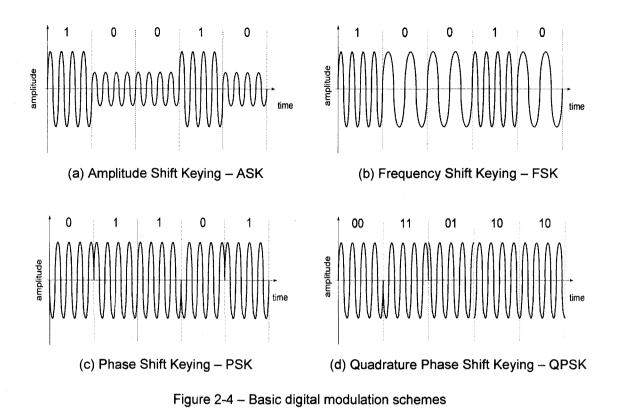

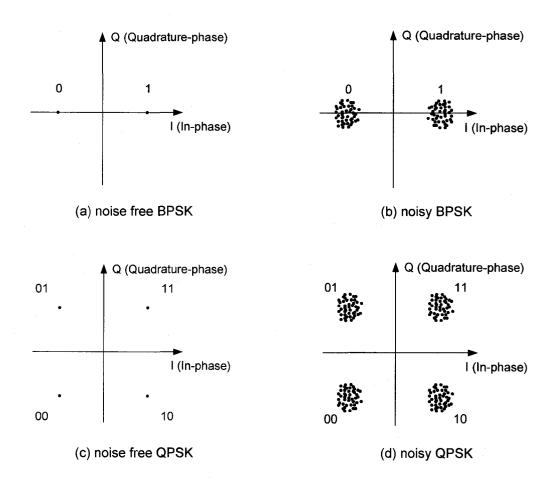

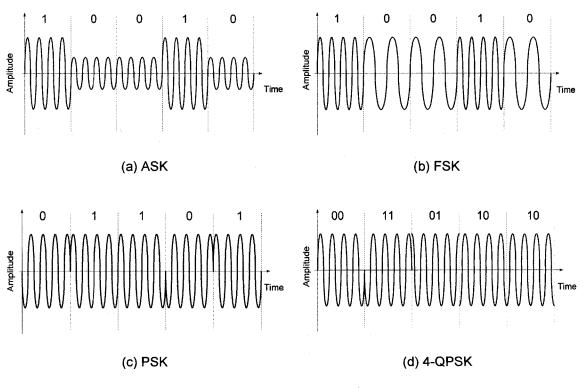

| Figure 2-4:  | Basic digital modulation schemes                             | 11 |

| Figure 2-5:  | Constellation diagram examples                               | 12 |

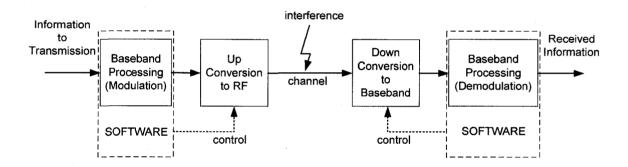

| Figure 2-6:  | Block diagram of a SDR communication system                  | 14 |

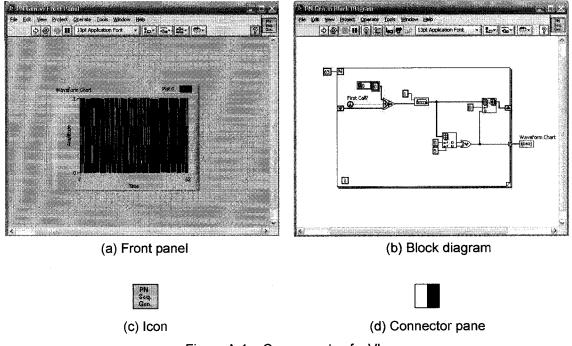

| Figure 2-7:  | Components of a VI                                           |    |

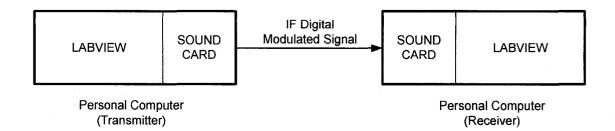

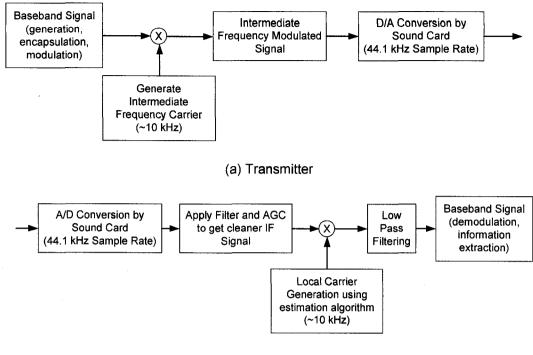

| Figure 2-8:  | SDR system using LabVIEW                                     | 18 |

| Figure 2-9:  | Signal path in the SDR system                                | 19 |

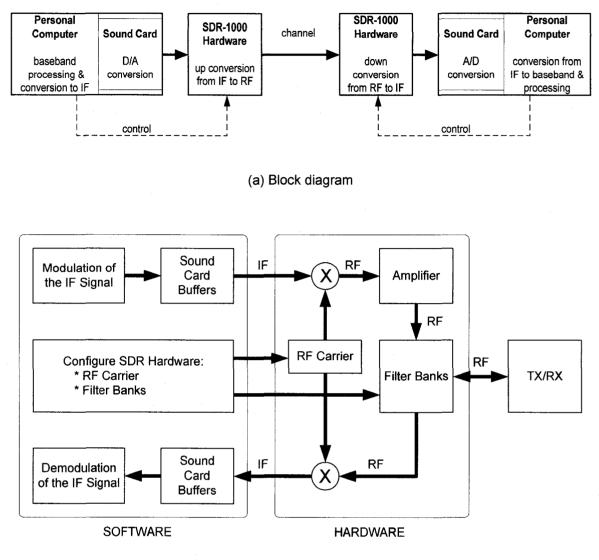

| Figure 2-10: | SDR system using RF front end hardware stage                 |    |

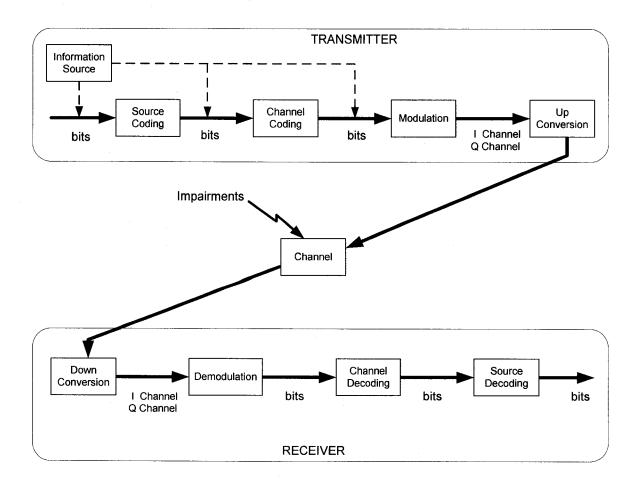

| Figure 3-1:  | Typical digital communication system block diagram           | 28 |

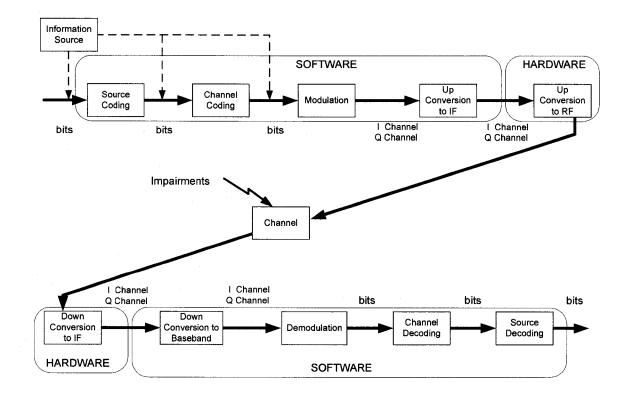

| Figure 3-2:  | Software and hardware implementation in a digital            |    |

| -            | communication system                                         | 32 |

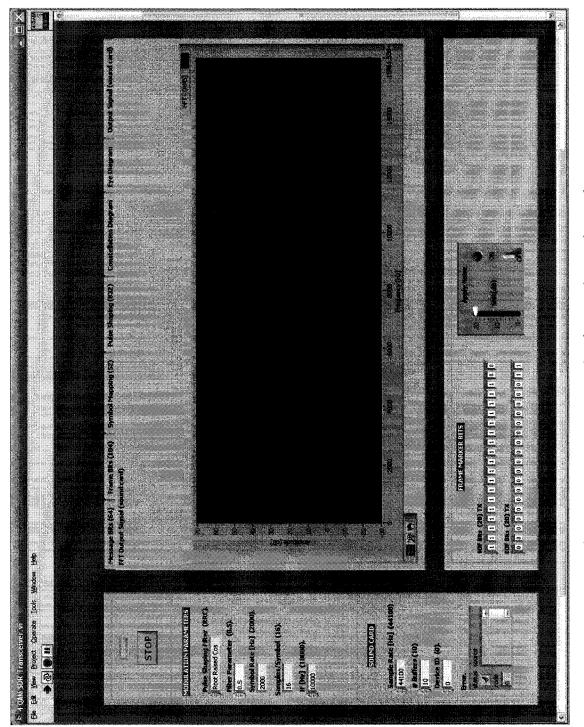

| Figure 4-1:  | 4 QAM SDR Transceiver front panel                            | 37 |

| Figure 4-2:  | VI's execution control                                       |    |

| Figure 4-3:  | Transmitter modulation parameters                            | 39 |

| Figure 4-4:  | Sound card parameters                                        |    |

| Figure 4-5:  | Graph display tabs for transmitter mode                      | 41 |

| Figure 4-6:  | Apply noise control                                          |    |

| Figure 4-7:  | Modulation parameters in receiver mode                       | 44 |

| Figure 4-8:  | Graph display tabs for receiver mode                         |    |

| Figure 4-9:  | RX status display                                            |    |

| Figure 4-10: | Time delay control                                           | 47 |

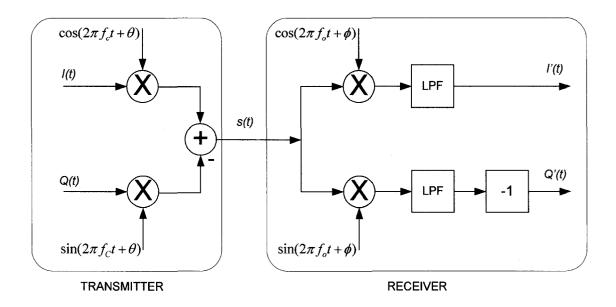

| Figure 5-1:  | Quadrature modulation and demodulation                       | 51 |

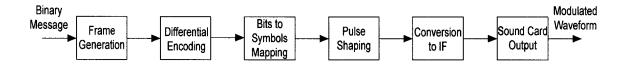

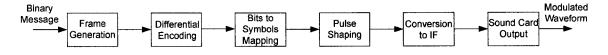

| Figure 5-2:  | Transmitter structure                                        | 53 |

| Figure 5-3:  | Frame structure                                              | 54 |

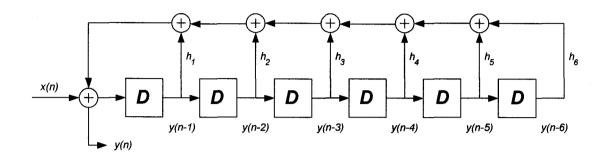

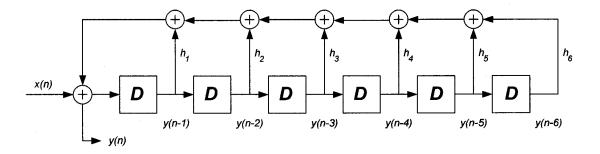

| Figure 5-4:  | PN generator with a six-stage linear feedback shift register |    |

| C            | structure                                                    | 55 |

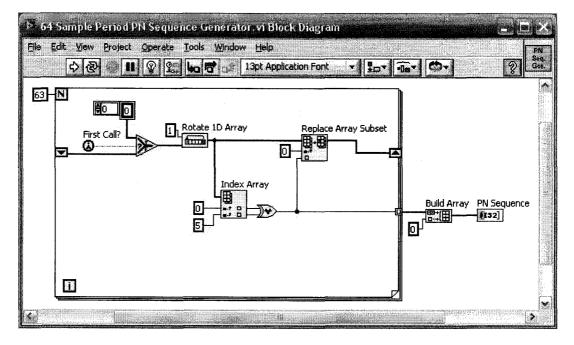

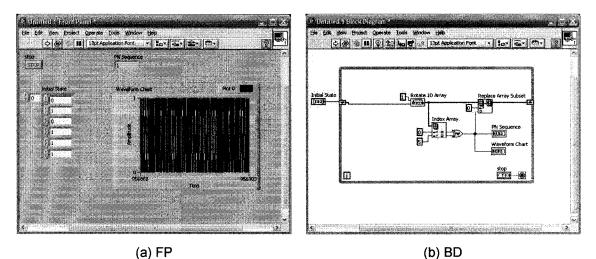

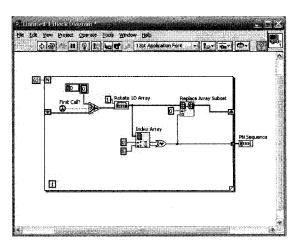

| Figure 5-5:  | 64 Sample Period PN Sequence Generator.vi                    | 57 |

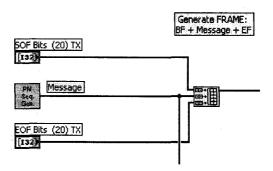

| Figure 5-6:  | Frame generation                                             |    |

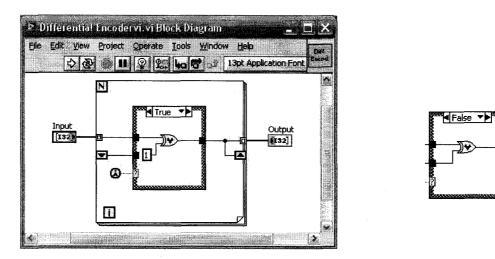

| Figure 5-7:  | Differential Encoder.vi                                      | 58 |

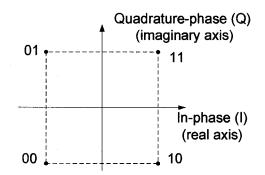

| Figure 5-8:  | 4 QAM constellation diagram                                  | 59 |

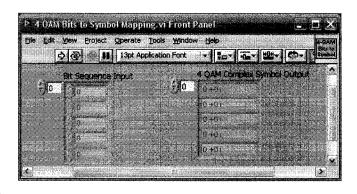

| Figure 5-9:  | 4 QAM Bits to Symbol Mapping.vi                              |    |

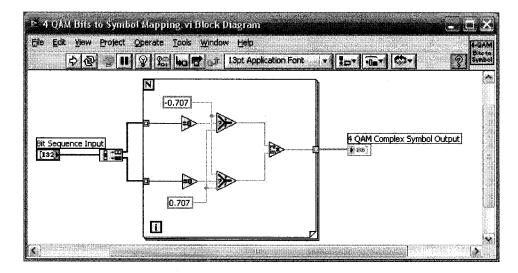

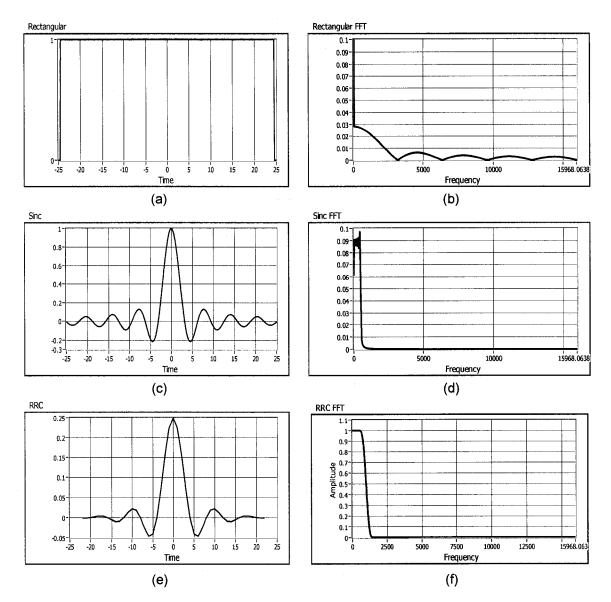

|              | Some pulse shapes in the time and frequency domains          |    |

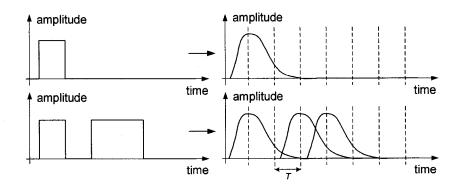

|              | Intersymbol interference (ISI)                               |    |

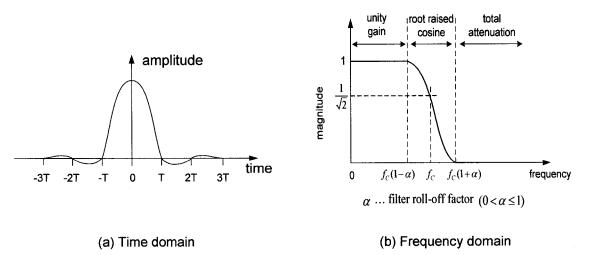

|              | Ideal root raised cosine response                            |    |

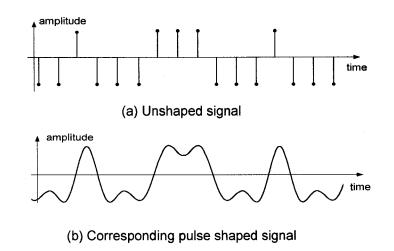

|              | Pulse shaping example                                        |    |

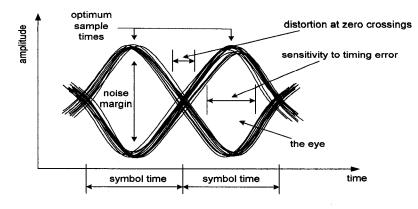

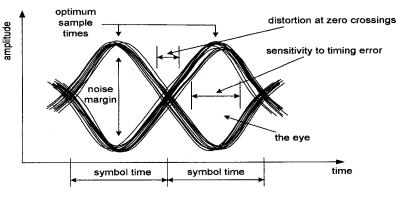

|              | Eye diagram                                                  |    |

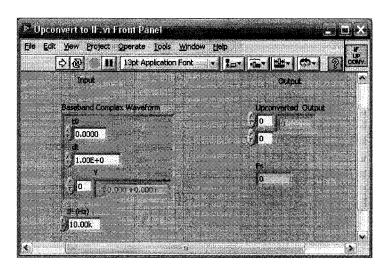

| Figure 5-15: | Upconvert to IF.vi                                           | 69 |

|              | Receiver structure                                           |    |

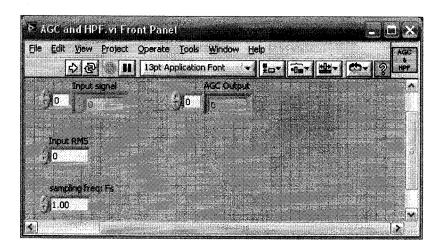

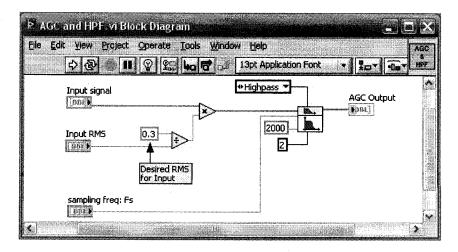

|              | AGC and HPF.vi                                               |    |

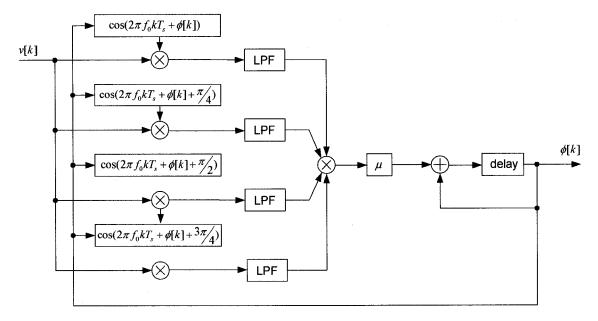

| Figure 5-18: | The 4 QAM Costas Loop algorithm                              | 79 |

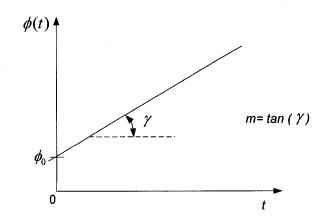

| Figure 5-19: | Phase update in the presence of frequency offset             | 80 |

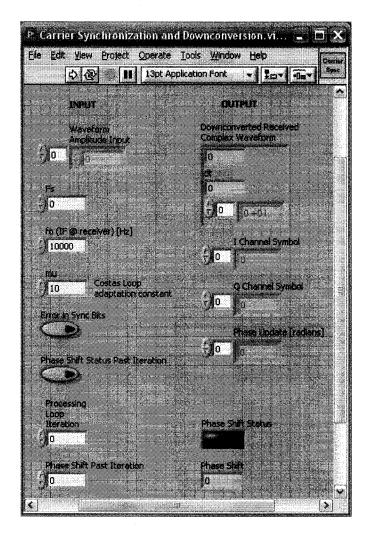

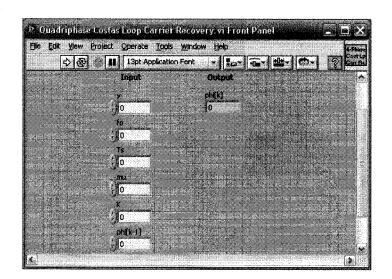

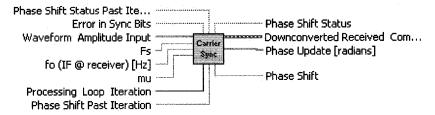

| Figure 5-20: | Carrier Synchronization and Downconversion.vi front panel    | 82 |

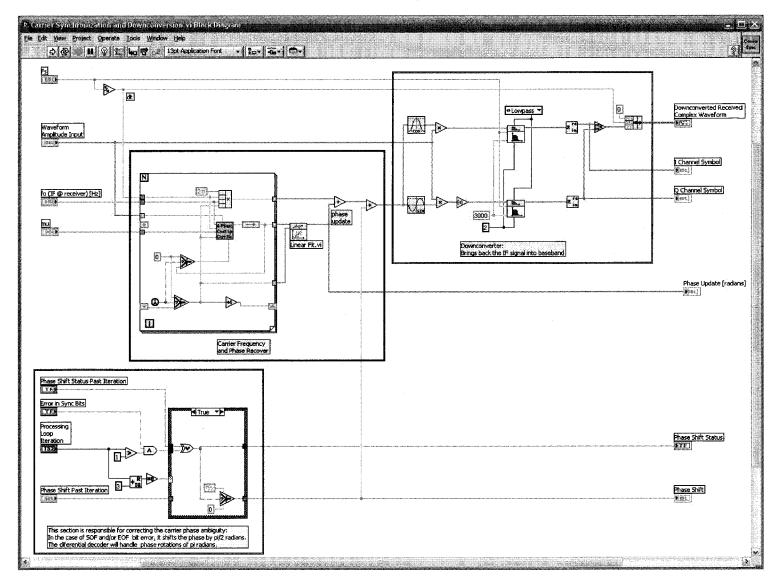

| Figure 5-21: | Carrier Synchronization and Downconversion.vi block diagram. | 83  |

|--------------|--------------------------------------------------------------|-----|

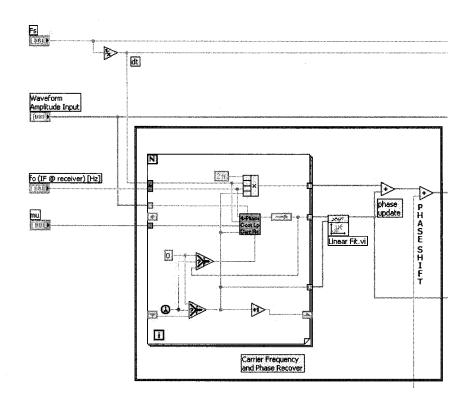

| Figure 5-22: | Carrier frequency and phase recovery part of Carrier         |     |

|              | Synchronization and Downconversion.vi                        | 84  |

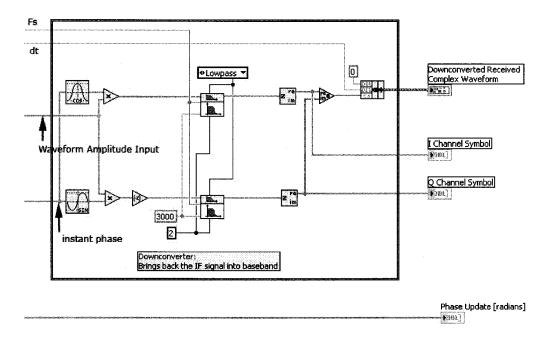

| Figure 5-23: | Down conversion part of Carrier Synchronization and          |     |

|              | Downconversion.vi                                            | 84  |

| Figure 5-24: | Phase ambiguity resolution of Carrier Synchronization and    |     |

|              | Downconversion.vi                                            |     |

|              | Quadriphase Costas Loop Carrier Recovery.vi                  |     |

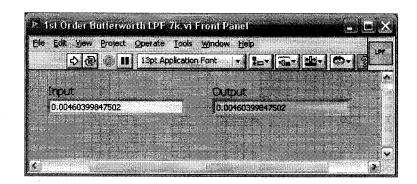

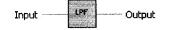

| -            | 1st Order Butterworth LPF 7k.vi                              |     |

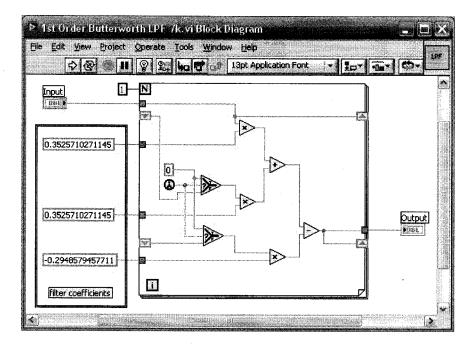

| •            | Symbol synchronization                                       |     |

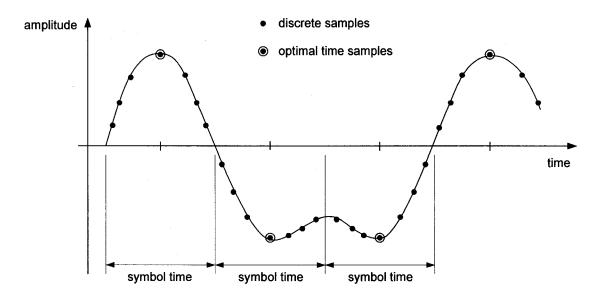

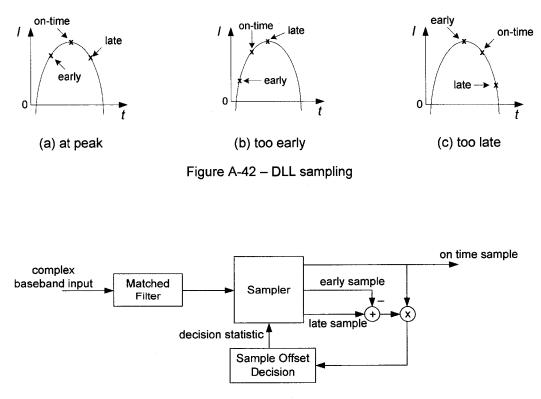

| •            | DLL sampling                                                 |     |

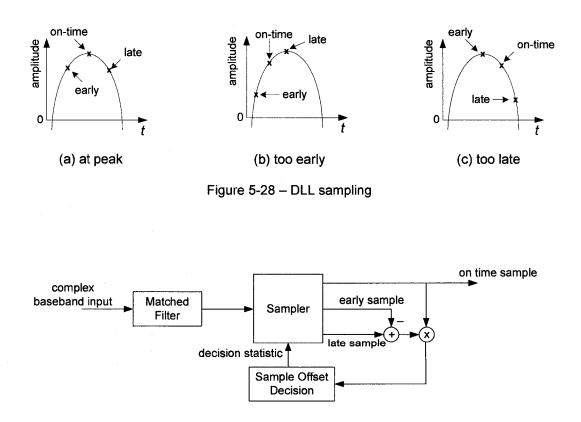

| •            | DLL block diagram                                            |     |

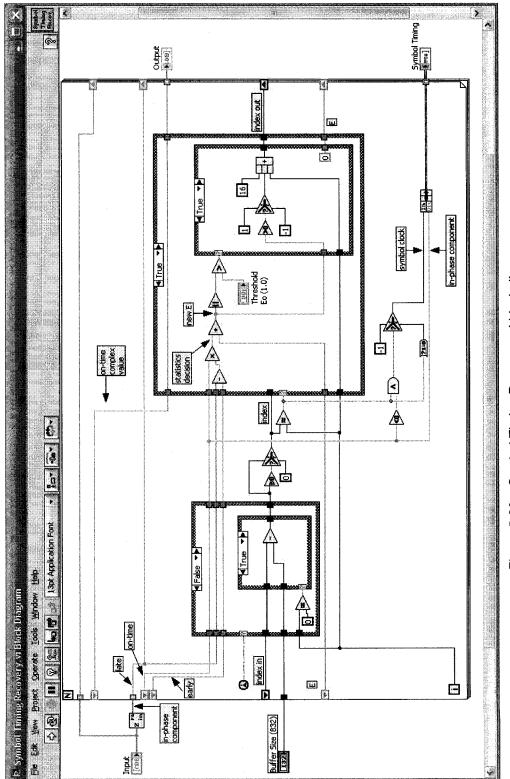

|              | Symbol Timing Recovery.vi block diagram                      | 92  |

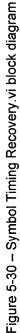

| Figure 5-31: | Symbol Timing Recovery.vi block diagram: detail of case      |     |

|              | structures                                                   |     |

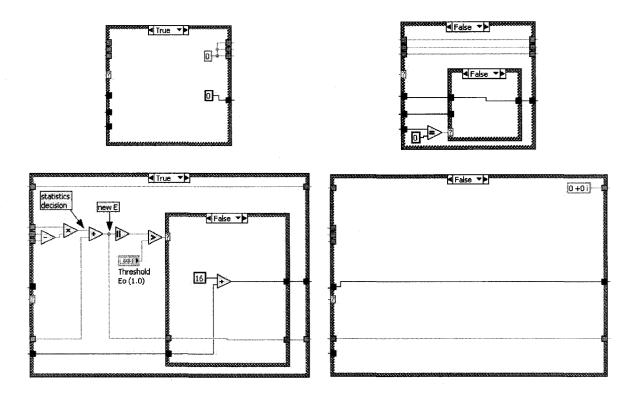

|              | Symbol Timing Recovery.vi front panel                        |     |

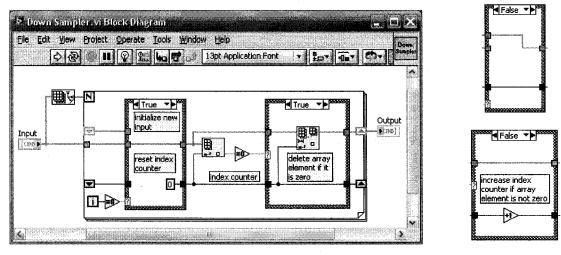

|              | Down Sampler.vi                                              |     |

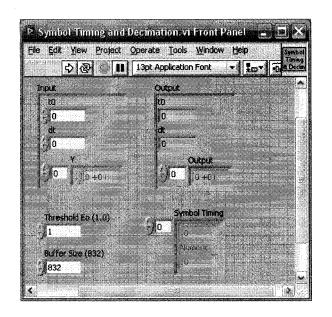

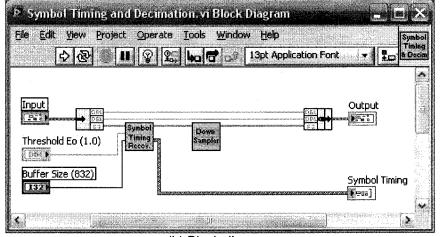

|              | Symbol Timing and Decimation.vi                              |     |

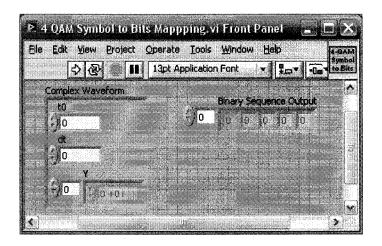

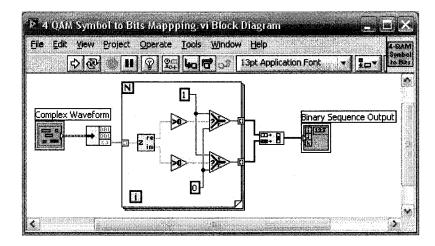

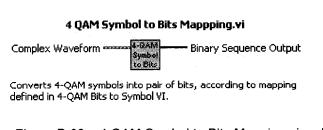

|              | 4 QAM Symbol to Bits.vi                                      |     |

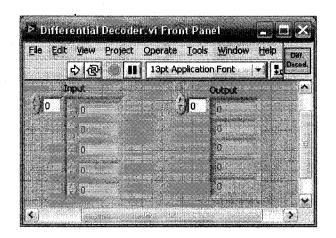

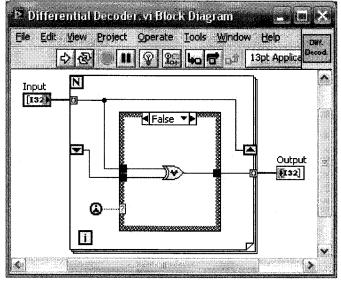

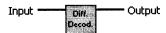

|              | Differential Decoder.vi                                      |     |

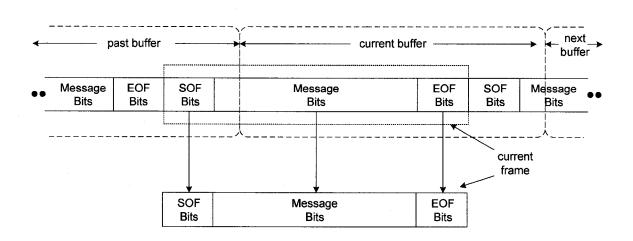

|              | Frame synchronization                                        |     |

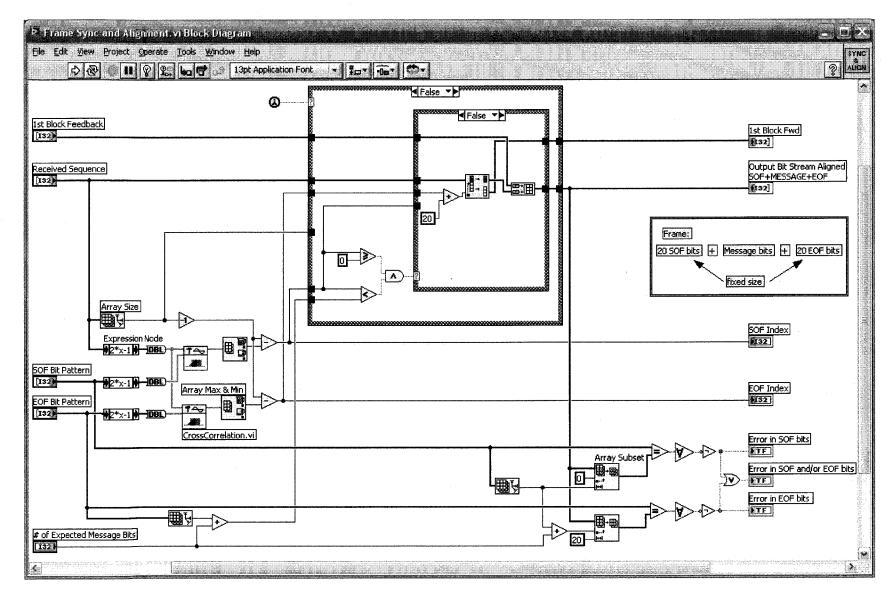

|              | Frame Sync and Alignment.vi block diagram                    | 102 |

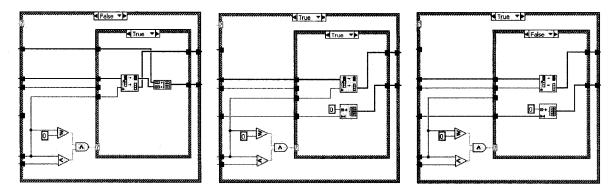

| Figure 5-39: | Frame Sync and Alignment.vi block diagram: case structures   |     |

|              | details                                                      |     |

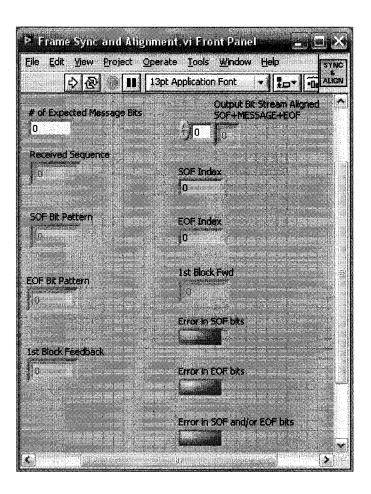

|              | Frame Sync and Alignment.vi front panel                      |     |

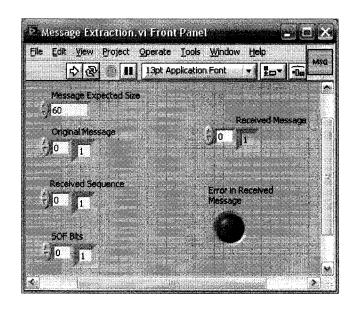

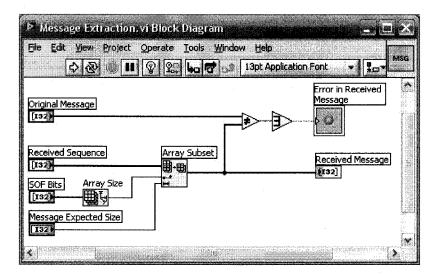

| -            | Message Extraction.vi                                        |     |

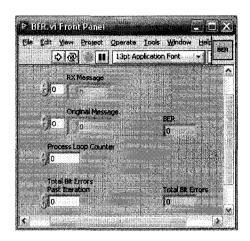

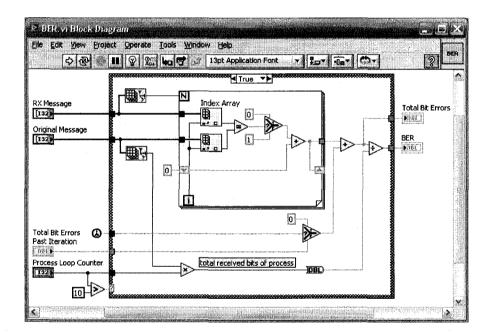

| •            | BER.vi                                                       |     |

| Figure A-1:  |                                                              | 117 |

| Figure A-2:  | PN generator with a six-stage linear feedback shift register |     |

|              | structure                                                    |     |

| Figure A-3:  | While Loop                                                   |     |

| Figure A-4:  | Creating stop button                                         |     |

| Figure A-5:  | Running the VI                                               |     |

| Figure A-6:  | Adding shift register                                        |     |

|              | Creating array control shell                                 |     |

|              | Initializing the shift register                              |     |

| Figure A-9:  | • •                                                          |     |

| •            | Inserting index array                                        |     |

|              | Wiring XOR function                                          |     |

|              | Inserting replace array subset                               |     |

|              | After initial state data type change                         |     |

|              | Inserting PN sequence indicator                              |     |

| -            | Running the VI with the waveform chart                       |     |

| -            | Moving waveform chart outside the loop                       |     |

|              | VI after enabling indexing                                   |     |

| Figure A-18: | For loop                                                     | 127 |

| Figure A-19: | Generation of 63 PN samples                               | 127 |

|--------------|-----------------------------------------------------------|-----|

| Figure A-20: | Final BD                                                  | 128 |

| Figure A-21: | Icon editor window                                        | 128 |

|              | VI connector pane                                         |     |

| Figure A-23: | Documenting the VI                                        | 129 |

| Figure A-24: | Context Help window                                       | 130 |

| Figure A-25: | Digital modulation schemes                                | 132 |

| Figure A-26: | Transmitter structure                                     | 133 |

| Figure A-27: | Receiver structure                                        | 134 |

|              | Frame structure                                           |     |

| Figure A-29: | 4 QAM constellation diagram                               | 135 |

| Figure A-30: | Ideal root raised cosine frequency response               | 136 |

|              | Frame synchronization                                     |     |

| Figure A-32: | Some pulse shapes in the time and frequency domains       | 145 |

| Figure A-33: | Intersymbol interference (ISI)                            | 146 |

| Figure A-34: | Ideal root raised cosine response                         | 146 |

| Figure A-35: | Pulse shaping example                                     | 147 |

|              | Eye diagram                                               |     |

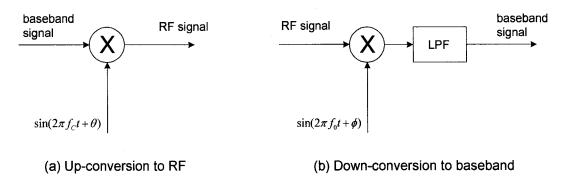

| Figure A-37: | Up and down conversion                                    | 151 |

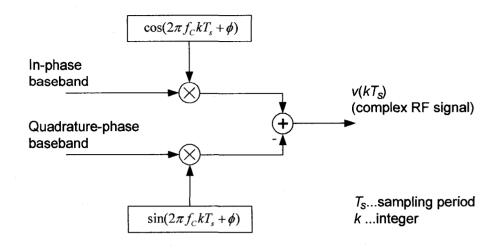

| Figure A-38: | Quadrature conversion to RF                               | 152 |

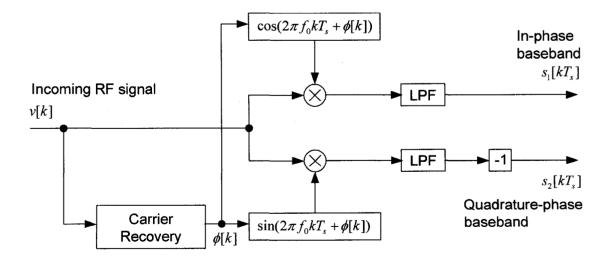

| Figure A-39: | Carrier recovery and down conversion                      | 152 |

|              | 4 QAM Costas Loop                                         |     |

| Figure A-41: | Phase update in the presence of frequency offset          | 154 |

| Figure A-42: | DLL sampling                                              | 159 |

| Figure A-43: | Delay-Locked Loop block diagram                           | 159 |

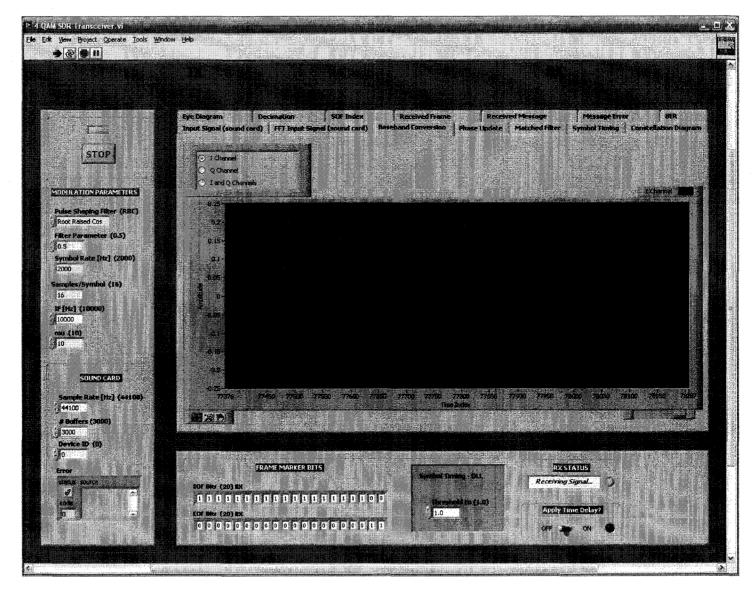

| Figure B-1:  | 4 QAM SDR Transceiver front panel: transmitter mode       | 164 |

| Figure B-2:  | 4 QAM SDR Transceiver front panel: receiver mode          | 165 |

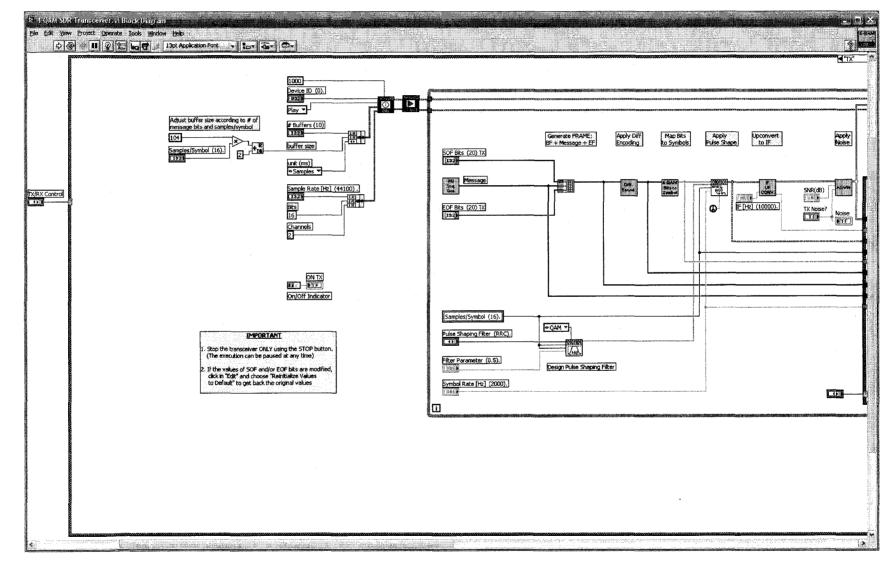

| Figure B-3:  | 4 QAM SDR Transceiver block diagram, transmitter mode:    |     |

|              | part 1                                                    | 166 |

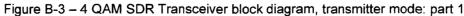

| Figure B-4:  | 4 QAM SDR Transceiver block diagram, transmitter mode:    |     |

|              |                                                           | 167 |

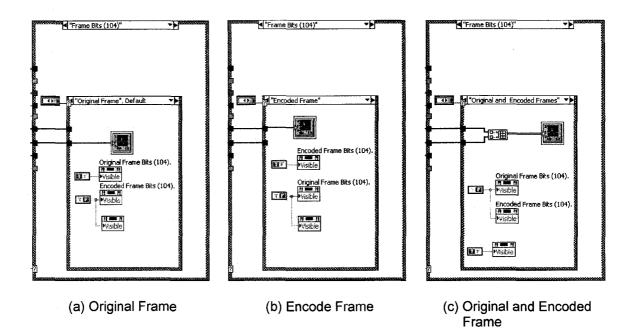

| Figure B-5:  | 4 QAM SDR Transceiver.vi BD, transmitter mode: Frame Bits |     |

|              | case structures                                           | 168 |

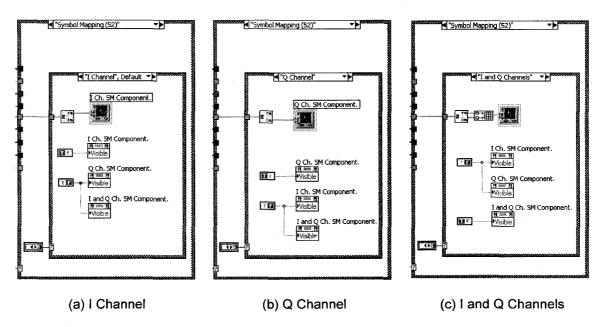

| Figure B-6:  | 4 QAM SDR Transceiver.vi BD, transmitter mode: Symbol     |     |

|              | Mapping case structures                                   | 168 |

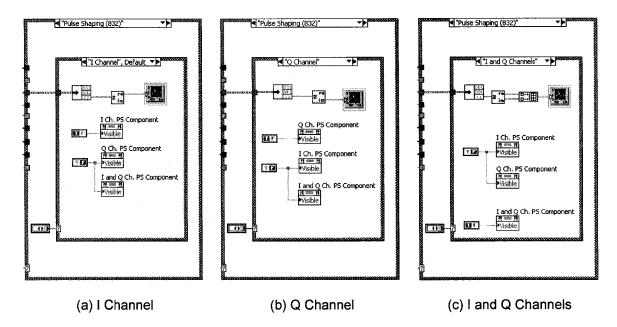

| Figure B-7:  | 4 QAM SDR Transceiver.vi BD, transmitter mode: Pulse      |     |

|              | Shaping case structures                                   | 169 |

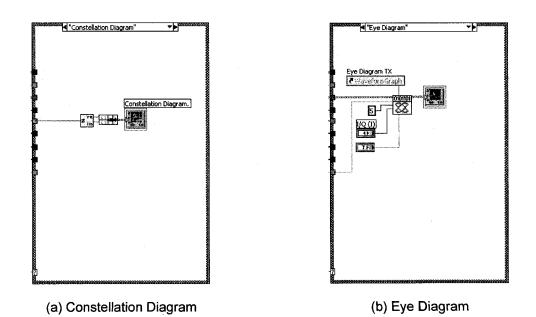

| Figure B-8:  | 4 QAM SDR Transceiver.vi BD, transmitter mode:            |     |

|              | Constellation and Eye diagrams structures                 | 169 |

| Figure B-9:  | 4 QAM SDR Transceiver.vi BD, transmitter mode: Output     |     |

|              | Signal and FFT Output Signal case structures              |     |

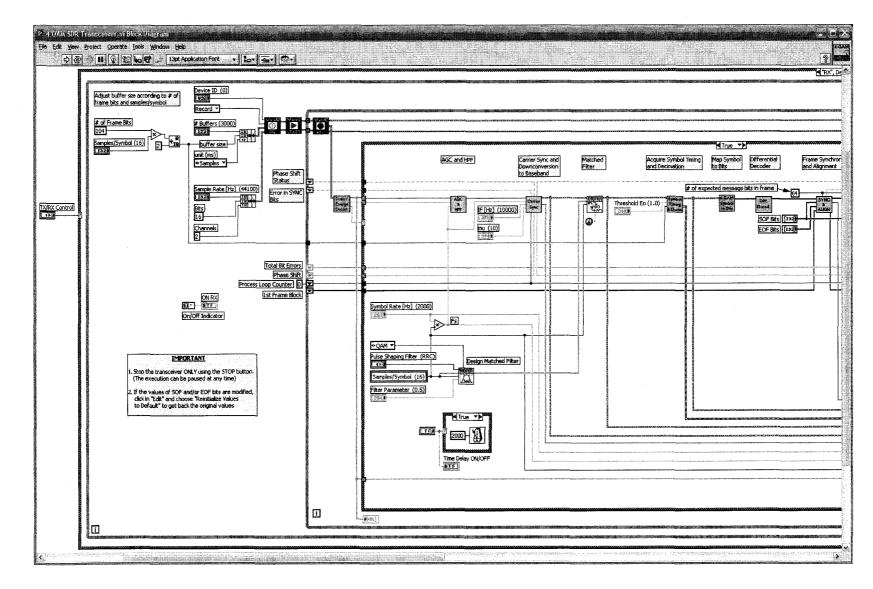

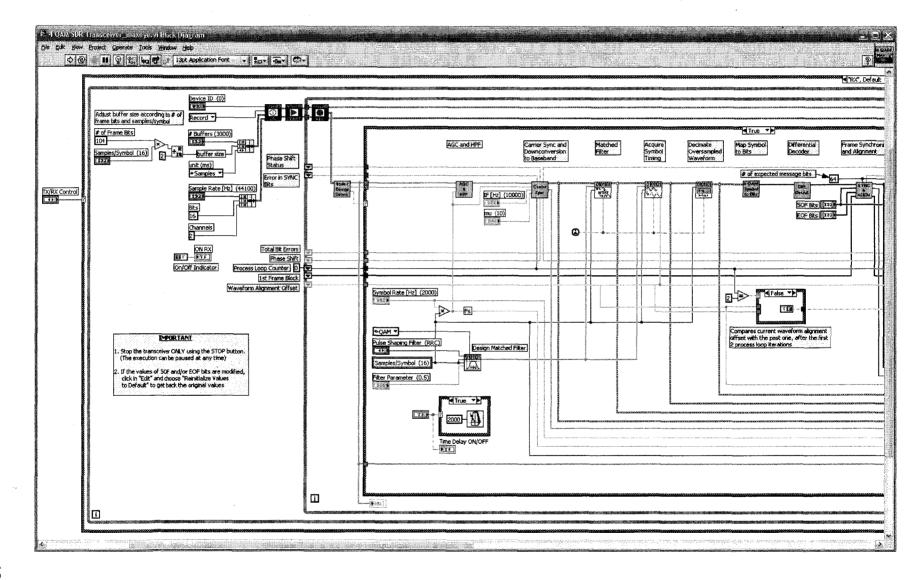

|              | 4 QAM SDR Transceiver.vi BD, receiver mode: part 1        |     |

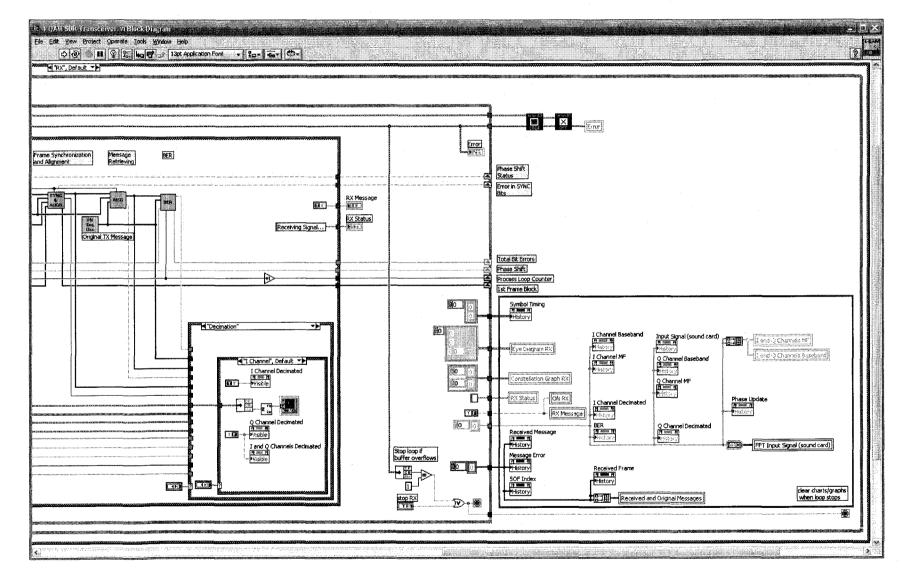

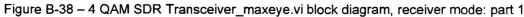

|              | 4 QAM SDR Transceiver.vi BD, receiver mode: part 2        | 172 |

| Figure B-12: | 4 QAM SDR Transceiver.vi block diagram, receiver          | 4=0 |

|              | mode: false case structure                                | 173 |

,

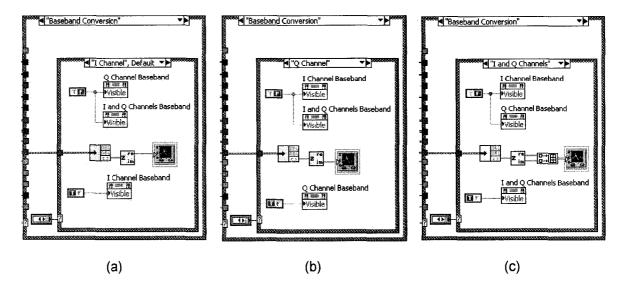

| Figure B-13:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Baseband                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                              | conversion case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 174                                                                                                   |

| Figure B-14:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Matched Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |

|                                                                                                                                                                                                                              | case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174                                                                                                   |

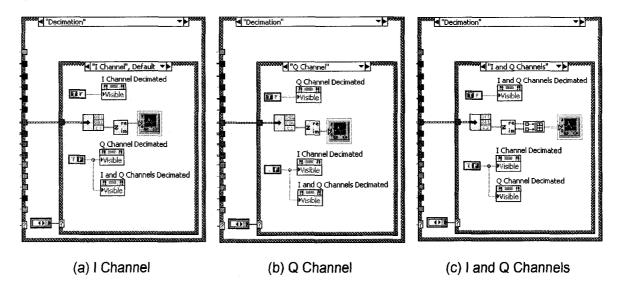

| Figure B-15:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Decimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 475                                                                                                   |

|                                                                                                                                                                                                                              | case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1/5                                                                                                   |

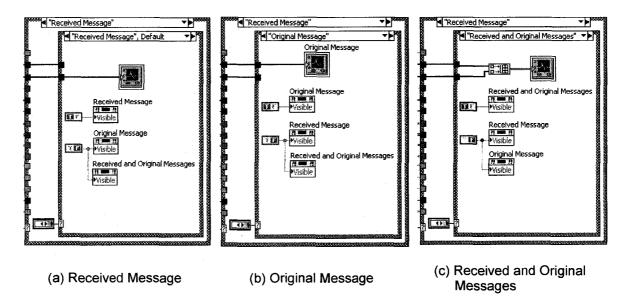

| Figure B-16:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 475                                                                                                   |

| <b>Einung D 47</b>                                                                                                                                                                                                           | Message case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 175                                                                                                   |

| Figure B-17:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: FFT Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 470                                                                                                   |

| / _                                                                                                                                                                                                                          | Signal, Phase Update, and Symbol Timing case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 176                                                                                                   |

| Figure B-18:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Constellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |

|                                                                                                                                                                                                                              | Diagram, Eye Diagram, and SOF Index case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 176                                                                                                   |

| Figure B-19:                                                                                                                                                                                                                 | 4 QAM SDR Transceiver.vi BD, receiver mode: Received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

|                                                                                                                                                                                                                              | Frame, Message Error, and BER case structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 177                                                                                                   |

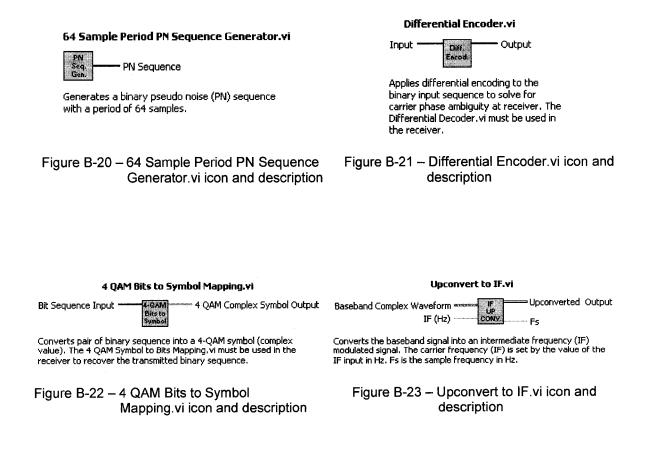

| Figure B-20:                                                                                                                                                                                                                 | 64 sample period PN Sequence Generator.vi icon and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

|                                                                                                                                                                                                                              | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

|                                                                                                                                                                                                                              | Differential Encoder.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|                                                                                                                                                                                                                              | 4 QAM Bits to Symbol Mapping.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

| Figure B-23:                                                                                                                                                                                                                 | Upconvert to IF.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 177                                                                                                   |

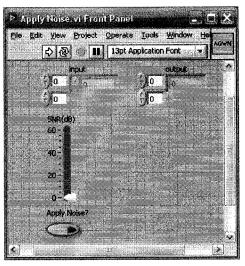

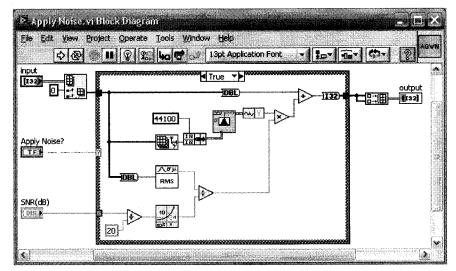

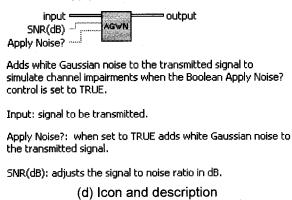

| Figure B-24:                                                                                                                                                                                                                 | Apply Noise.vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 178                                                                                                   |

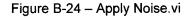

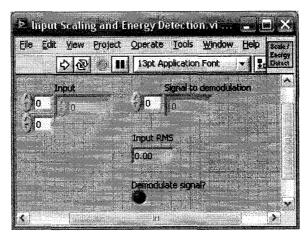

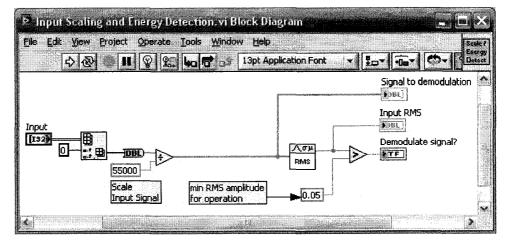

| Figure B-25:                                                                                                                                                                                                                 | Input Scaling and Energy Detection.vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 179                                                                                                   |

|                                                                                                                                                                                                                              | AGC and HPF.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|                                                                                                                                                                                                                              | <b>.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| Figure B-27:                                                                                                                                                                                                                 | Carrier Synchronization and Downconversion vincon and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| Figure B-27:                                                                                                                                                                                                                 | Carrier Synchronization and Downconversion.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 180                                                                                                   |

| -                                                                                                                                                                                                                            | description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 180                                                                                                   |

| -                                                                                                                                                                                                                            | description<br>Quadriphase Costas Loop Carrier Recover vi icon and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

| Figure B-28:                                                                                                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 181                                                                                                   |

| Figure B-28:<br>Figure B-29:                                                                                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 181<br>181                                                                                            |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:                                                                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 181<br>181<br>181                                                                                     |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:                                                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 181<br>181<br>181<br>182                                                                              |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:                                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 181<br>181<br>181<br>182<br>182                                                                       |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:                                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description<br>4 QAM Symbol to Bits Mapping.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 181<br>181<br>181<br>182<br>182<br>182                                                                |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-34:                                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description<br>4 QAM Symbol to Bits Mapping.vi icon and description<br>Differential Decoder.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 181<br>181<br>181<br>182<br>182<br>182<br>182                                                         |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-34:<br>Figure B-35:                                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description<br>4 QAM Symbol to Bits Mapping.vi icon and description<br>Differential Decoder.vi icon and description<br>Frame Synchronization and Alignment.vi icon and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 181<br>181<br>182<br>182<br>182<br>182<br>182<br>183                                                  |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-34:<br>Figure B-35:<br>Figure B-36:                                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description<br>4 QAM Symbol to Bits Mapping.vi icon and description.<br>Differential Decoder.vi icon and description<br>Frame Synchronization and Alignment.vi icon and description.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 181<br>181<br>182<br>182<br>182<br>182<br>182<br>183<br>183                                           |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-33:<br>Figure B-34:<br>Figure B-35:<br>Figure B-36:<br>Figure B-37:                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description.<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description.<br>4 QAM Symbol to Bits Mapping.vi icon and description.<br>Differential Decoder.vi icon and description.<br>Frame Synchronization and Alignment.vi icon and description.<br>BER.vi icon and description.                                                                                                                                                                                                                                                                                                                                                                                                                           | 181<br>181<br>182<br>182<br>182<br>182<br>182<br>183<br>183                                           |

| Figure B-28:<br>Figure B-29:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-33:<br>Figure B-34:<br>Figure B-35:<br>Figure B-36:<br>Figure B-37:                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description<br>4 QAM Symbol to Bits Mapping.vi icon and description<br>Differential Decoder.vi icon and description<br>Frame Synchronization and Alignment.vi icon and description<br>BER.vi icon and description<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver                                                                                                                                                                                                                                                                                                                                                                      | 181<br>181<br>182<br>182<br>182<br>182<br>183<br>183<br>183                                           |

| Figure B-28:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-33:<br>Figure B-35:<br>Figure B-36:<br>Figure B-37:<br>Figure B-38:                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description.<br>Symbol Timing and Decimation.vi icon and description.<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description.<br>4 QAM Symbol to Bits Mapping.vi icon and description.<br>Differential Decoder.vi icon and description.<br>Frame Synchronization and Alignment.vi icon and description.<br>BER.vi icon and description.<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver<br>mode: part 1                                                                                                                                                                                                                                                                                                                                               | 181<br>181<br>182<br>182<br>182<br>182<br>183<br>183<br>183                                           |

| Figure B-28:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-33:<br>Figure B-35:<br>Figure B-36:<br>Figure B-37:<br>Figure B-38:                                                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description.<br>Symbol Timing and Decimation.vi icon and description.<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description.<br>4 QAM Symbol to Bits Mapping.vi icon and description.<br>Differential Decoder.vi icon and description.<br>Frame Synchronization and Alignment.vi icon and description.<br>BER.vi icon and description.<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver<br>mode: part 1<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver                                                                                                                                                                                                                                                                                    | 181<br>181<br>182<br>182<br>182<br>182<br>183<br>183<br>183<br>184                                    |

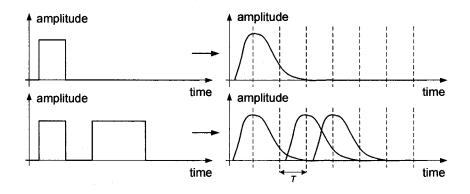

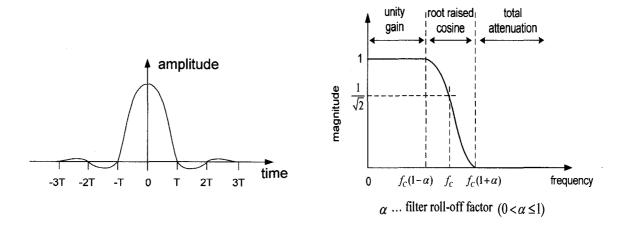

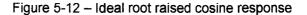

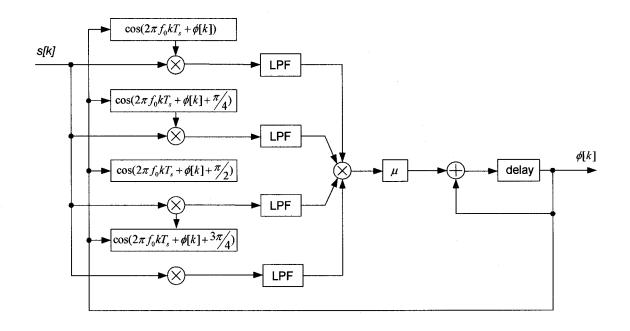

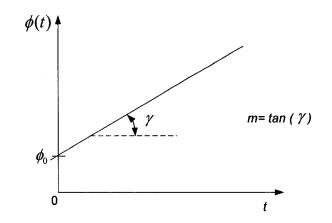

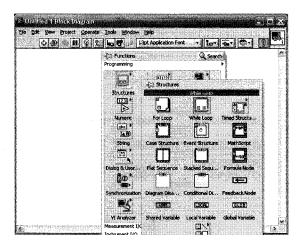

| Figure B-28:<br>Figure B-30:<br>Figure B-30:<br>Figure B-31:<br>Figure B-32:<br>Figure B-33:<br>Figure B-34:<br>Figure B-35:<br>Figure B-36:<br>Figure B-37:<br>Figure B-38:<br>Figure B-39:                                 | description<br>Quadriphase Costas Loop Carrier Recover.vi icon and<br>description<br>1st Order Butterworth LPF 7k.vi icon and description.<br>Symbol Timing and Decimation.vi icon and description<br>Symbol Timing Recovery.vi icon and description<br>Down Sampler.vi icon and description.<br>4 QAM Symbol to Bits Mapping.vi icon and description.<br>Differential Decoder.vi icon and description.<br>Frame Synchronization and Alignment.vi icon and description.<br>BER.vi icon and description<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver<br>mode: part 1<br>4 QAM SDR Transceiver_maxeye.vi block diagram, receiver<br>mode: part 2                                                                                                                                                                                                                                                                      | 181<br>181<br>182<br>182<br>182<br>182<br>183<br>183<br>183<br>184                                    |